# 8-1 High-speed Counter Board

## 8-1-1 Model

| Name                     | Model       | Specification                              |

|--------------------------|-------------|--------------------------------------------|

| High-speed Counter Board | CQM1H-CTB41 | Four pulse inputs                          |

|                          |             | Four external outputs of comparison result |

## 8-1-2 Functions

The High-speed Counter Board is an Inner Board that handles four pulse inputs.

#### High-speed Counter Pulse Inputs 1 to 4

The High-speed Counter Board counts high-speed pulses from 50 to 500 kHz entering through ports 1 to 4, and performs tasks according to the number of pulses counted.

#### Input Modes

The following three Input Modes are available:

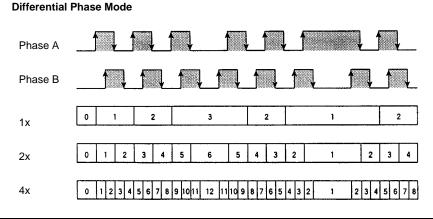

- Differential Phase Mode (1x/2x/4x)

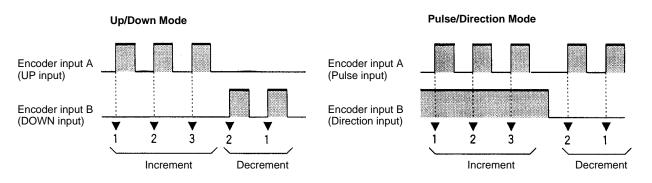

- Up/Down Mode

- Pulse/Direction Mode

#### **Comparison Operation**

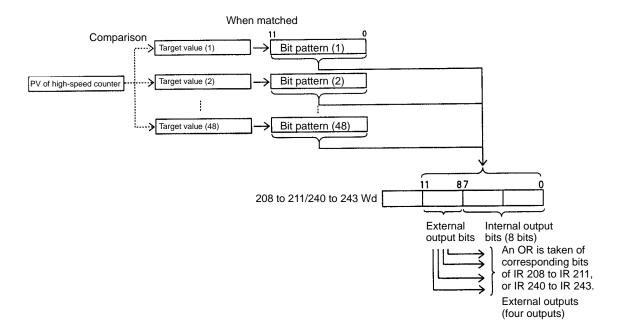

When the PV (present value) of the high-speed counter matches a specified target value or lies within a specified range, the bit pattern specified in the comparison table is stored in internal output bits and external output bits. A bit pattern can be set for each comparison result, and the external output bits can be output through an external output terminal as described below.

#### **External Outputs**

Up to four external outputs can be produced when either the target value is matched or a range comparison condition is satisfied.

**Note** The High-speed Counter Board does not provide high-speed counter interrupts. It simply compares the PV to target values or comparison ranges, and produces internal and external bit outputs.

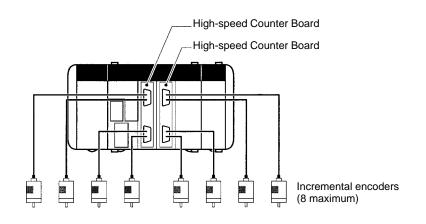

## 8-1-3 Example System Configuration

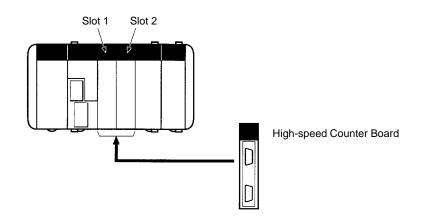

## 8-1-4 Applicable Inner Board Slots

The High-speed Counter Board can be installed in either slot 1 (left slot) or slot 2 (right slot) of the CQM1H-CPU51/61 CPU Unit. Both slots can be used at the same time.

## 8-1-5 Names and Functions

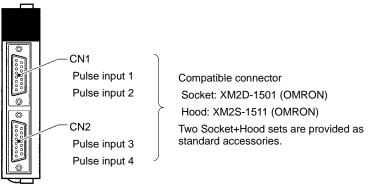

One High-speed Counter Board provides two connectors that accept highspeed pulse inputs. CN1 is used for inputs 1 and 2, and CN2 is used for inputs 3 and 4.

#### **LED Indicators**

#### **RDY: Operational (Green)**

RDY

ERR □ B1

A1

**Z1**

Lit when pulse inputs can be received. Pulse Inputs (Orange) A1, A2, A3, A4: Lit when phase-A input is ON in port 1, 2, 3, or 4. A2 A3 A4 B2 B3 B4 Z2 Z3 Z4 2 3 4 B1, B2, B3, B4: Lit when phase-B input is ON in port 1, 2, 3, or 4. Z1, Z2, Z3, Z4: Lit when phase-Z input is ON in port 1, 2, 3, or 4. **External Outputs (Orange)** OUT1, OUT2, OUT3, OUT4: Lit when the corresponding output (1, 2, 3, or 4) is ON. ERR: Error (Red)

Lit when an error is detected in the PC Setup settings for the input pulse function, or when an overflow or underflow occurs in the high-speed counter's present value.

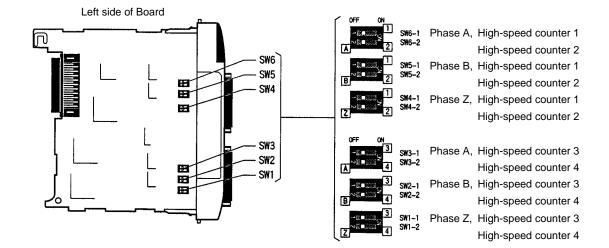

## Input Voltage Level Switches

| Counter 1 | Counter 2 | Counter 3 | Counter 4 | Status | Setting                        |                            |  |

|-----------|-----------|-----------|-----------|--------|--------------------------------|----------------------------|--|

| SW6-1     | SW6-2     | SW3-1     | SW3-2     | ON     | Counter input: Input voltage A | Line driver level          |  |

|           |           |           |           | OFF    |                                | 24-V DC level<br>(default) |  |

| SW5-1     | SW5-2     | SW2-1     | SW2-2     | ON     | Counter input: Input voltage B | Line driver level          |  |

|           |           |           |           | OFF    |                                | 24-V DC level<br>(default) |  |

| SW4-1     | SW4-2     | SW1-1     | SW1-2     | ON     | Counter input: Input voltage Z | Line driver level          |  |

|           |           |           |           | OFF    |                                | 24-V DC level<br>(default) |  |

## 8-1-6 Pin Arrangement of Connectors CN1 and CN2

#### CN1: Pulse Input 1 and 2

| Pin arrangement | Pin No. | Name | Function                                               |

|-----------------|---------|------|--------------------------------------------------------|

| 8               | 1       | 2OUT | External output 2                                      |

| 15              | 2       | 10UT | External output 1                                      |

|                 | 3       | 1Z–  | Counter 1 input: Z –                                   |

|                 | 4       | 1Z+  | Counter 1 input: Z +                                   |

|                 | 5       | 1B–  | Counter 1 input: B –                                   |

|                 | 6       | 1B+  | Counter 1 input: B +                                   |

|                 | 7       | 1A-  | Counter 1 input: A –                                   |

|                 | 8       | 1A+  | Counter 1 input: A +                                   |

|                 | 9       | +DC  | Power supply for external outputs 1 to 4: 5 to 24 V DC |

| 9               | 10      | 2Z–  | Counter 2 input: Z –                                   |

|                 | 11      | 2Z+  | Counter 2 input: Z +                                   |

|                 | 12      | 2B-  | Counter 2 input: B –                                   |

|                 | 13      | 2B+  | Counter 2 input: B +                                   |

|                 | 14      | 2A-  | Counter 2 input: A –                                   |

|                 | 15      | 2A+  | Counter 2 input: A +                                   |

|                 | Hood    | NC   | Not used.                                              |

#### CN2: Pulse Input 3 and 4

| Pin arrangement                       | Pin No. | Name | Function                                      |

|---------------------------------------|---------|------|-----------------------------------------------|

| 8                                     | 1       | 3Z-  | Counter 3 input: Z –                          |

| 15                                    | 2       | 3Z+  | Counter 3 input: Z +                          |

|                                       | 3       | 3B-  | Counter 3 input: B –                          |

|                                       | 4       | 3B+  | Counter 3 input: B +                          |

|                                       | 5       | 3A-  | Counter 3 input: A –                          |

|                                       | 6       | 3A+  | Counter 3 input: A –                          |

|                                       | 7       | 4OUT | External output 4                             |

|                                       | 8       | 3OUT | External output 3                             |

|                                       | 9       | 4Z-  | Counter 4 input: Z –                          |

| i i i i i i i i i i i i i i i i i i i | 10      | 4Z+  | Counter 4 input: Z +                          |

|                                       | 11      | 4B-  | Counter 4 input: B –                          |

|                                       | 12      | 4B+  | Counter 4 input: B +                          |

|                                       | 13      | 4A-  | Counter 4 input: A –                          |

|                                       | 14      | 4A+  | Counter 4 input: A +                          |

|                                       | 15      | –DC  | Power supply for external outputs 1 to 4: 0 V |

|                                       | Hood    | NC   | Not used.                                     |

**Note** Refer to *Appendix A Preparing Cables for Inner Boards* for information about using a compatible connector (XM2D-1501 Socket with XM2S-1511 Hood) to construct a cable.

## 8-1-7 Wiring Examples

**Pulse Input Connections**

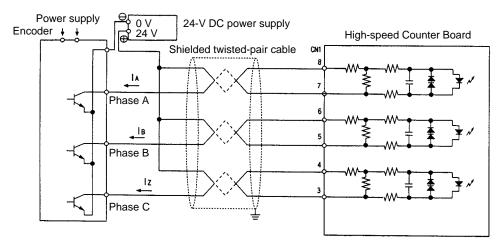

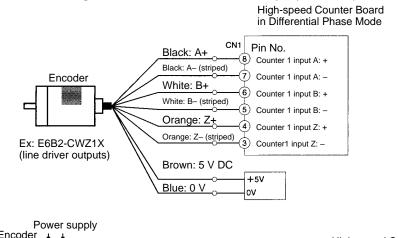

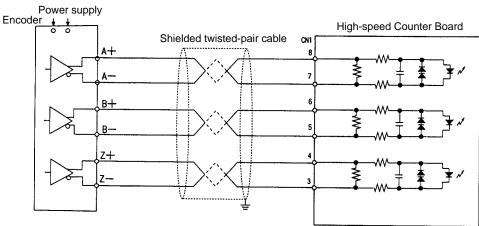

Connect the encoder outputs to CN1 and CN2 as shown below according to the port's Input Mode.

| CN1    | pins    | CN2    | pins    | Signal name     | Encoder output             |                             |                          |

|--------|---------|--------|---------|-----------------|----------------------------|-----------------------------|--------------------------|

| Port 1 | Port 2  | Port 3 | Port 4  |                 | Differential<br>Phase Mode | Pulse/Direction<br>Mode     | Up/Down Mode             |

| 8 (7)  | 15 (14) | 6 (5)  | 14 (13) | Encoder input A | Encoder phase<br>A input   | Pulse input                 | Increment pulse<br>input |

| 6 (5)  | 13 (12) | 4 (3)  | 12 (11) | Encoder input B | Encoder phase<br>B input   | Directional<br>signal input | Decrement<br>pulse input |

**Note** Pin numbers for negative pins are given in parentheses.

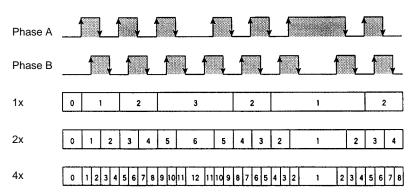

#### **Differential Phase Mode**

## High-speed Counter Board

| Phase A      | Phase B      | 1x         | 2x         | 4x         |

|--------------|--------------|------------|------------|------------|

| $\uparrow$   | L            | Count up   | Count up   | Count up   |

| Н            | $\uparrow$   |            |            | Count up   |

| $\downarrow$ | Н            |            | Count up   | Count up   |

| L            | $\downarrow$ |            |            | Count up   |

| L            | $\uparrow$   |            |            | Count down |

| $\uparrow$   | Н            |            | Count down | Count down |

| Н            | $\downarrow$ |            |            | Count down |

| $\downarrow$ | L            | Count down | Count down | Count down |

**Note** The function of encoder inputs A and B in Pulse/Direction Mode and Up/Down Mode differs from the Pulse I/O Board (CQM1H-PLB21).

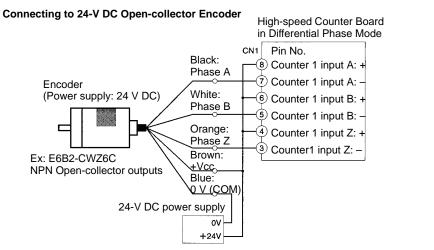

#### Wiring Examples

The following diagrams show a connection to an encoder possessing phases A, B, and Z.

(Do not share the power supply with other I/O.)

#### Connecting to an Encoder with a Line-driver Output (Am26LS31)

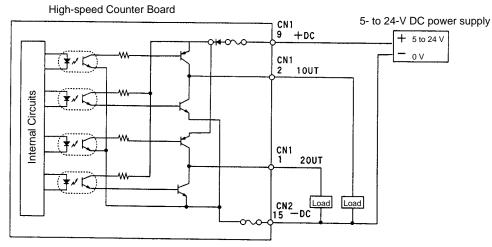

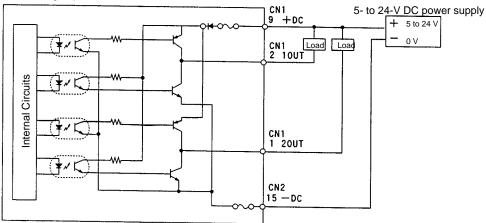

#### External Output Connections

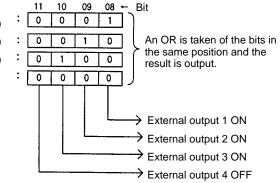

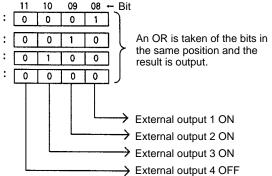

The comparison results of high-speed counters 1 to 4 generate four external bit patterns. An OR is taken of corresponding bits in these 4-bit patterns, and the result is then output on external outputs 1 to 4. The bit patterns are set by the user when programming the comparison operation.

| Connector | Pin no. | Name | Content                                              |

|-----------|---------|------|------------------------------------------------------|

| CN1       | 2       | 10UT | External output 1                                    |

|           | 1       | 20UT | External output 2                                    |

|           | 9       | +DC  | Power supply for external outputs<br>1 to 4: 24 V DC |

| CN2       | 8       | 3OUT | External output 3                                    |

|           | 7       | 40UT | External output 4                                    |

|           | 15      | -DC  | Power supply for external outputs 1 to 4: 0 V        |

**Note** Switching between sourcing (PNP) outputs and sinking (NPN) outputs is accomplished using the PC Setup (DM 6602, DM 6611).

#### Example External Output Lines

#### Sourcing (PNP) Output

#### Sinking (NPN) Outputs

High-speed Counter Board

# 8-1-8 Specifications

| ltem                                                  | Specifications                                                                                                          |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Name                                                  | High-speed Counter Board                                                                                                |

| Model number                                          | CQM1H-CTB41                                                                                                             |

| Applicable CPU Units                                  | CQM1H-CPU51/61                                                                                                          |

| Unit classificatiion                                  | CQM1H-series Inner Board                                                                                                |

| Mounting locations and number of Boards               | Maximum of two Boards can be mounted simultaneously in slots 1 and 2.                                                   |

| Pulse inputs                                          | 4 inputs (Refer to <i>High-speed Counter Specifications</i> below for details.)                                         |

| External outputs                                      | 4 outputs (Refer to <i>External Output Specifications</i> below for details.)                                           |

| Settings                                              | Input voltage level switch                                                                                              |

| Indicators                                            | Front: 18 LEDs                                                                                                          |

|                                                       | 1 each of Ready (RDY) and Error (ERR)<br>4 each of phase A (A□), phase B (B□), phase Z (Z□), and external output (OUT□) |

| Front connections                                     | Connectors CN1 and CN2 (Compatible connectors: Sockets & Hoods provided as standard accessories.)                       |

| Current consumption (Supplied from Power Supply Unit) | 5 V DC 400 mA max.                                                                                                      |

| Dimensions                                            | $25 \times 110 \times 107 \text{ mm} (W \times H \times D)$                                                             |

| Weight                                                | 90 g max.                                                                                                               |

| Standard accessories                                  | Sockets: XM2D-1501 (OMRON) x 2<br>Hoods: XM2S-1511 (OMRON) x 2                                                          |

# High-speed Counter Specifications

## **Counter Specifications**

| ltem                               |              |                              |                                                                                                                |                        | Specifications                                                      |                                |                                |

|------------------------------------|--------------|------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------|--------------------------------|--------------------------------|

| Number of counters                 |              | 4 counters (ports)           |                                                                                                                |                        |                                                                     |                                |                                |

| Input Modes (Set in the PC Setup.) |              | Differential Phase<br>Inputs | Up/Down Pulse Inputs                                                                                           | Pulse/Direction Inputs |                                                                     |                                |                                |

| Input                              | Port 1       | Port 2                       | Port 3                                                                                                         | Port 4                 |                                                                     | •                              |                                |

| pin<br>No.                         | 8 (7)        | 15 (14)                      | 6 (5)                                                                                                          | 14 (13)                | Phase-A input                                                       | Increment pulse input          | Pulse input                    |

| NO.                                | 6 (5)        | 13 (12)                      | 4 (3)                                                                                                          | 12 (11)                | Phase-B input                                                       | Decrement pulse input          | Direction input                |

|                                    | 4 (3)        | 11 (10)                      | 2 (1)                                                                                                          | 10 (9)                 | Phase-Z input                                                       | Reset input                    | Reset input                    |

| Input ı                            | Input method |                              | Switching between<br>inputs using phase<br>difference multiples of<br>1x, 2x, or 4x. (Set in<br>the PC Setup.) | 2, single-phase inputs | Single-phase pulse<br>and direction inputs                          |                                |                                |

| Count<br>PC Se                     |              | cy (Set for                  | each port                                                                                                      | in the                 | 25 kHz (default) or 250<br>kHz                                      | 50 kHz (default) or 500<br>kHz | 50 kHz (default) or 500<br>kHz |

| Count                              | Count value  |                              |                                                                                                                |                        | Linear Mode:<br>-8388608 to 8388607 BCD, F8000000 to 07FFFFFF Hex   |                                |                                |

|                                    |              |                              |                                                                                                                |                        | BCD, 00000000 to 07FFF<br>set to within the range 1 t<br>CTBL(63).) |                                |                                |

|                                | Item               | Specifications                                                                                                                                                                                                                                                                                  |

|--------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

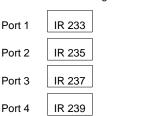

| Storage location of counter PV |                    | When mounted in slot 1:<br>Port 1: IR 201 (leftmost digits) and IR 200 (rightmost digits)<br>Port 2: IR 203 (leftmost digits) and IR 202 (rightmost digits)<br>Port 3: IR 205 (leftmost digits) and IR 204 (rightmost digits)<br>Port 4: IR 207 (leftmost digits) and IR 206 (rightmost digits) |

|                                |                    | When mounted in slot 2:<br>Port 1: IR 233 (leftmost digits) and IR 232 (rightmost digits)<br>Port 2: IR 235 (leftmost digits) and IR 234 (rightmost digits)<br>Port 3: IR 237 (leftmost digits) and IR 236 (rightmost digits)<br>Port 4: IR 239 (leftmost digits) and IR 238 (rightmost digits) |

|                                |                    | Data format: 8-digit BCD or 8-digit Hex<br>(Set in the PC Setup: Bits 00 to 03 of DM 6602/DM 6611.)                                                                                                                                                                                             |

|                                |                    | Linear Mode:<br>F8388608 to 8388607 BCD (Leftmost digit is F Hex for negative numbers.)<br>F8000000 to 07FFFFFF Hex                                                                                                                                                                             |

|                                |                    | Ring Mode:<br>00000000 to 08388607 BCD<br>00000000 to 07FFFFF Hex                                                                                                                                                                                                                               |

| Control                        | Target value match | Up to 48 target values and external/internal output bit patterns registered.                                                                                                                                                                                                                    |

| method                         | Range comparison   | Up to 16 upper limits, lower limits, and external/internal output bit patterns registered.                                                                                                                                                                                                      |

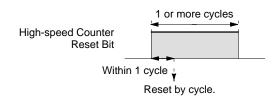

| Counter reset method           |                    | Phase-Z Signal + Software Reset<br>A counter is reset on the first phase-Z signal input after its Reset Bit (see<br>below) is turned ON.                                                                                                                                                        |

|                                |                    | Software Reset<br>A counter is reset when its Reset Bit (see below) is turned ON.                                                                                                                                                                                                               |

|                                |                    | Reset Bits<br>IR 21200 to IR 21203 (For ports 1 to 4 in slot 1)<br>AR 0500 to AR 0503 (For ports 1 to 4 in slot 2)                                                                                                                                                                              |

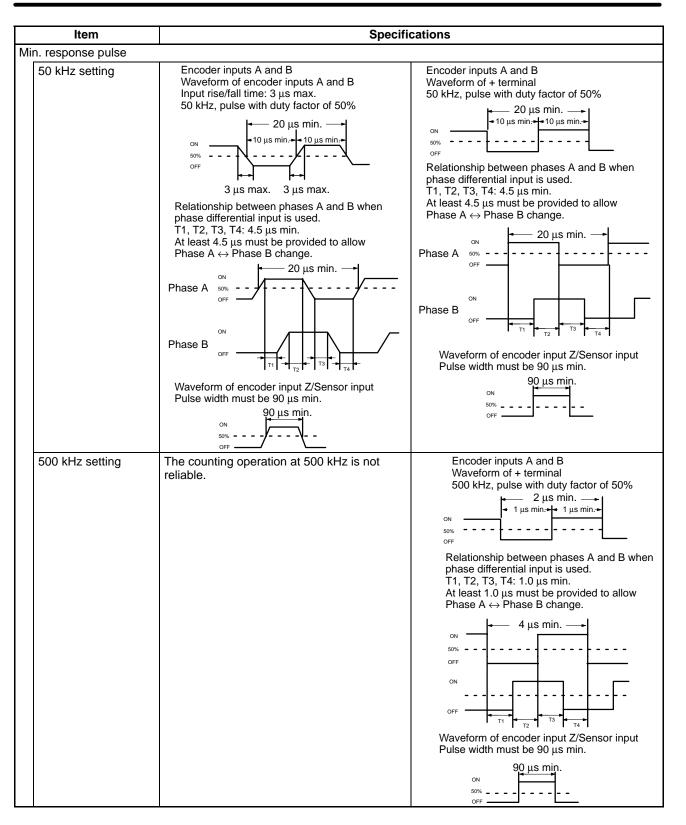

## **Pulse Input Specifications**

| Item                   | Specifications                                                                                        |                         |                                              |               |  |

|------------------------|-------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------------------|---------------|--|

| Number of pulse inputs | 4 inputs (Ports 1 to 4 =                                                                              | = High-speed counters 1 | to 4)                                        |               |  |

| Signals                | Encoder inputs A and                                                                                  | B; pulse input Z        |                                              |               |  |

| Input voltage          | Switched by means of input voltage switch on the Board (Specified separately for phases A, B, and Z.) |                         |                                              |               |  |

|                        | 24 V DC±10%                                                                                           |                         | RS-422A line driver (AM26LS31 or equivalent) |               |  |

|                        | Phase A and B                                                                                         | Phase Z                 | Phase A and B                                | Phase Z       |  |

| Input current          | 5 mA typical                                                                                          | 8 mA typical            | 10 mA typical                                | 13 mA typical |  |

| ON voltage             | 19.6 V DC min. 18.6 V DC min.                                                                         |                         |                                              |               |  |

| OFF voltage            | 4.0 V DC min.                                                                                         | 4.0 V DC min.           |                                              |               |  |

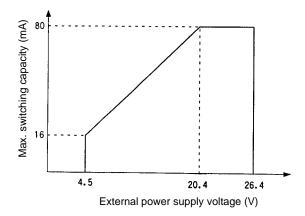

## **External Output Specifications**

| Item                         | Specifications                                                                                                                                                                                                                                         |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of external outputs   | 4 transistor outputs<br>(Four outputs set together for sinking or sourcing outputs: Set in PC Setup)                                                                                                                                                   |

| Function                     | The target comparison or range comparison results of high-speed counters 1 to 4 output four user-defined 4-bit external bit patterns. An OR is taken of corresponding bits in these bit patterns, and the result is output on external outputs 1 to 4. |

|                              | Note External outputs 1 to 4 can be turned ON using IR 21300 to IR 21303 and AR 0600 to AR 0603.                                                                                                                                                       |

| External power supply        | 5 to 24 V DC±10%                                                                                                                                                                                                                                       |

| Switching capacity           | 16 mA/4.5 V DC to 80 mA/26.4 V (see note)                                                                                                                                                                                                              |

| Leakage current              | 0.1 mA max.                                                                                                                                                                                                                                            |

| Residual voltage             | 0.8 V max.                                                                                                                                                                                                                                             |

| Response for target matching | 0.1 ms (This is the time required from completing target comparison until the external outputs are turned ON or OFF. The response time listed below must also be added.)                                                                               |

| Response time                | ON response: 0.1 ms max.; OFF response: 0.4 ms max.                                                                                                                                                                                                    |

**Note** The switching capacity is shown below.

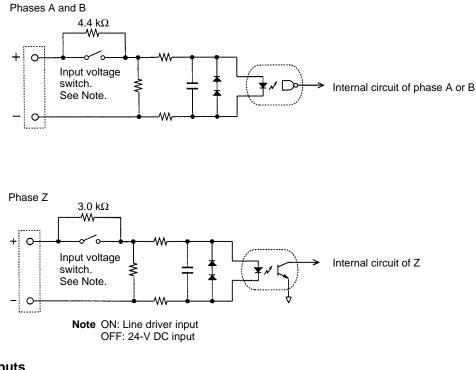

## 8-1-9 Internal Circuits

#### **Pulse Inputs**

#### **External Outputs**

**Note** In the above figure, A is active when sourcing outputs are set, and B is active when sinking outputs are set.

# 8-2 Pulse I/O Board

## 8-2-1 Model

| Name            | Model       | Specifications                                     |

|-----------------|-------------|----------------------------------------------------|

| Pulse I/O Board | CQM1H-PLB21 | Two pulse input points and two pulse output points |

## 8-2-2 Function

The Pulse I/O Board is an Inner Board that supports two pulse inputs and two pulse outputs.

Pulse Inputs 1 and 2

Pulse inputs 1 and 2 can be used as high-speed counters to count pulses input at either 50 kHz (signal phase) or 25 kHz (differential phase). Interrupt processing

can be performed based on the present values (PV) of the counters.

#### Input Mode

The following three Input Modes are available:

• Differential Phase Mode (4x)

# 2-1-6 Specifications

#### Instructions

| Instruction | Meaning                                                                                                                                                                                                                                    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTBL(63)    | Used to register target or range comparison tables or used to<br>start comparisons for previously registered comparison tables. A<br>table can be registered and comparison started with separate<br>instructions or the same instruction. |

| INI(61)     | Used to start or stop comparison using registered comparison table or used to change the PV of a high-speed counter.                                                                                                                       |

| PRV(62)     | Used to read the PV or status of a high-speed counter.                                                                                                                                                                                     |

## Related Control Bits, Flags, and Status Information

| W                                 | ord                               | Bits     | Name                                                 |                                 | Function                                                                                                                 |

|-----------------------------------|-----------------------------------|----------|------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Slot 1                            | Slot 2                            |          |                                                      |                                 |                                                                                                                          |

| IR 200                            | IR 232                            | 00 to 15 | Counter 1                                            | PV (rightmost four digits)      | The PV of the high-speed counter on                                                                                      |

| IR 201                            | IR 233                            | 00 to 15 |                                                      | PV (leftmost four digits)       | each port of the High-speed Counter<br>Board is stored after each cycle.                                                 |

| IR 202                            | IR 234                            | 00 to 15 | Counter 2                                            | PV (rightmost four digits)      | ,                                                                                                                        |

| IR 203                            | IR 235                            | 00 to 15 |                                                      | PV (leftmost four digits)       | Note The form in which data is stored (BCD or hexadecimal) can be speci-                                                 |

| IR 204                            | IR 236                            | 00 to 15 | Counter 3                                            | PV (rightmost four digits)      | fied in the PC Setup (DM 6602 and                                                                                        |

| IR 205                            | IR 237                            | 00 to 15 |                                                      | PV (leftmost four digits)       | DM 6611).                                                                                                                |

| IR 206                            | IR 238                            | 00 to 15 | Counter 4                                            | PV (rightmost four digits)      |                                                                                                                          |

| IR 207                            | IR 239                            | 00 to 15 |                                                      | PV (leftmost four digits)       |                                                                                                                          |

| IR 208:<br>Counter 1<br>IR 209:   | IR 240:<br>Counter 1<br>IR 241:   | 00 to 07 | Comparison Results: Internal Output<br>Bits 00 to 07 |                                 | Contains the bit pattern specified by operand in CTBL(63) when a condition is satisfied.                                 |

| Counter 2<br>IR 210:              | Counter 2<br>IR 242:              | 08 to 11 | Comparisor<br>Outputs 1 to                           | Results: Bits for External<br>4 | Contains the bit pattern specified by operand in CTBL(63) when a condition is satisfied.                                 |

| Counter 3<br>IR 211:<br>Counter 4 | Counter 3<br>IR 243:<br>Counter 4 | 12       | Counter Op                                           | erating Flag                    | 0: Stopped<br>1: Operating                                                                                               |

|                                   |                                   | 13       | Comparisor                                           | n Flag                          | Indicates whether or not a comparison is<br>in progress.<br>0: Stopped<br>1: Operating                                   |

|                                   |                                   | 14       | PV Overflow/Underflow Flag                           |                                 | Indicates whether or not an overflow or<br>underflow has occurred.<br>0: Normal<br>1: Overflow or underflow has occurred |

|                                   |                                   | 15       | SV Error Fla                                         | ag                              | 0: Normal<br>1: Setting error                                                                                            |

## Section 2-1

| W      | Word   |                               | Name                                         | Function                                                                                                                                                                                                                                     |

|--------|--------|-------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Slot 1 | Slot 2 |                               |                                              |                                                                                                                                                                                                                                              |

| IR 212 | AR 05  | 00                            | High-speed counter 1 Reset Bit               | Phase Z and software reset<br>0: Counter not reset on phase Z                                                                                                                                                                                |

|        |        | 01                            | High-speed counter 2 Reset Bit               | 1: Counter reset on phase Z                                                                                                                                                                                                                  |

|        |        | 02                            | High-speed counter 3 Reset Bit               | Software reset only<br>0: Counter not reset                                                                                                                                                                                                  |

|        |        | 03                            | High-speed counter 4 Reset Bit               | $0 \rightarrow 1$ : Counter reset                                                                                                                                                                                                            |

|        |        | 08                            | High-speed Counter 1 Comparison<br>Start Bit | $0 \rightarrow 1$ : Comparison starts<br>$1 \rightarrow 0$ : Comparison stops                                                                                                                                                                |

|        |        | 09                            | High-speed Counter 2 Comparison<br>Start Bit |                                                                                                                                                                                                                                              |

|        |        | 10                            | High-speed Counter 3 Comparison<br>Start Bit |                                                                                                                                                                                                                                              |

|        |        | 11                            | High-speed Counter 4 Comparison<br>Start Bit |                                                                                                                                                                                                                                              |

|        | 12     | High-speed Counter 1 Stop Bit | 0: Operation continues                       |                                                                                                                                                                                                                                              |

|        |        | 13                            | High-speed Counter 2 Stop Bit                | 1: Operation stops                                                                                                                                                                                                                           |

|        |        | 14                            | High-speed Counter 3 Stop Bit                |                                                                                                                                                                                                                                              |

|        |        | 15                            | High-speed Counter 4 Stop Bit                |                                                                                                                                                                                                                                              |

| IR 213 | AR 06  | 00                            | External Output 1 Force-set Bit              | 0: No effect on output status                                                                                                                                                                                                                |

|        |        | 01                            | External Output 2 Force-set Bit              | 1: Forces output ON                                                                                                                                                                                                                          |

|        |        | 02                            | External Output 3 Force-set Bit              |                                                                                                                                                                                                                                              |

|        |        | 03                            | External Output 4 Force-set Bit              |                                                                                                                                                                                                                                              |

|        |        | 04                            | External Output Force-set Enable Bit         | 0: Force-setting of outputs 1 to 4 disabled<br>1: Force-setting of outputs 1 to 4 enabled                                                                                                                                                    |

| SR 254 |        | 15                            | Inner Board Error Flag                       | 0: No error<br>1: Error<br>Turns ON when an error occurs in an<br>Inner Board mounted in slot 1 or slot 2.<br>The error code for slot 1 is stored in<br>AR 0400 to AR 0407 and the error code<br>for slot 2 is stored in AR 0408 to AR 0415. |

| AR 04  |        | 00 to 07                      | Error code for Inner Board in slot 1         | 00 Hex: Normal<br>01 or 02 Hex: Hardware error                                                                                                                                                                                               |

|        |        | 08 to 15                      | Error code for Inner Board in slot 2         | 03 Hex: PC Setup error                                                                                                                                                                                                                       |

## **Related PC Setup Settings**

| v               | Vord    | Bits     | Function                                                                                                                                                                                                            | When setting is          |

|-----------------|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Slot 1          | Slot 2  |          |                                                                                                                                                                                                                     | read                     |

| DM 6602 DM 6611 |         | 00 to 03 | Data format in which PVs of high-speed counters 1 to<br>4 are stored<br>0: Eight-digit hexadecimal (BIN)<br>1: Eight-digit BCD                                                                                      | When power is turned ON. |

|                 |         | 04 to 07 | Not used.                                                                                                                                                                                                           |                          |

|                 |         | 08 to 11 | Sourcing/Sinking setting for external outputs 1 to 4<br>0: Sourcing (PNP)<br>1: Sinking (NPN)                                                                                                                       |                          |

|                 |         | 12 to 15 | Not used.                                                                                                                                                                                                           |                          |

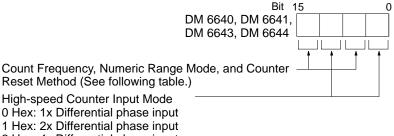

| DM 6640 DM 6643 |         | 00 to 03 | Input Mode for high-speed counter 1<br>0 Hex: 1x Differential phase input<br>1 Hex: 2x Differential phase input<br>2 Hex: 4x Differential phase input<br>3 Hex: Up/Down pulse input<br>4 Hex: Pulse/Direction input | When operation starts.   |

|                 |         | 04 to 07 | Count frequency, Numeric Range Mode and counter reset method of high-speed counter 1. Refer to the following table.                                                                                                 |                          |

|                 |         | 08 to 11 | Input Mode of high-speed counter 2<br>(Refer to the explanation given above for high-speed<br>counter 1.)                                                                                                           |                          |

|                 |         | 12 to 15 | Count frequency, Numeric Range Mode, and counter<br>reset method of high-speed counter 2<br>(Refer to the explanation given above for high-speed<br>counter 1.)                                                     |                          |

| DM 6641         | DM 6644 | 00 to 03 | Input Mode of high-speed counter 3<br>(Refer to the explanation given above for high-speed<br>counter 1.)                                                                                                           |                          |

|                 |         | 04 to 07 | Count frequency, Numeric Range Mode, and counter<br>reset method of high-speed counter 3<br>(Refer to the explanation given above for high-speed<br>counter 1.)                                                     |                          |

|                 |         | 08 to 11 | Input Mode of high-speed counter 4<br>(Refer to the explanation given above for high-speed<br>counter 1.)                                                                                                           | ]                        |

|                 |         | 12 to 15 | Count frequency, Numeric Range Mode, and counter<br>reset method of high-speed counter 4<br>(Refer to the explanation given above for high-speed<br>counter 1.)                                                     |                          |

## Count Frequency, Numeric Range Mode, and Counter Reset Method of High-speed Counters

| Value | Count frequency | Numeric Range Mode | Counter reset method     |

|-------|-----------------|--------------------|--------------------------|

| 0 Hex | 50 KHz          | Linear Mode        | Phase Z + software reset |

| 1 Hex |                 |                    | Software reset only      |

| 2 Hex |                 | Ring Mode          | Phase Z + software reset |

| 3 Hex |                 |                    | Software reset only      |

| 4 Hex | 500 KHz         | Linear Mode        | Phase Z + software reset |

| 5 Hex |                 |                    | Software reset only      |

| 6 Hex |                 | Ring Mode          | Phase Z + software reset |

| 7 Hex |                 |                    | Software reset only      |

## 2-1-7 High-speed Counters 1 to 4

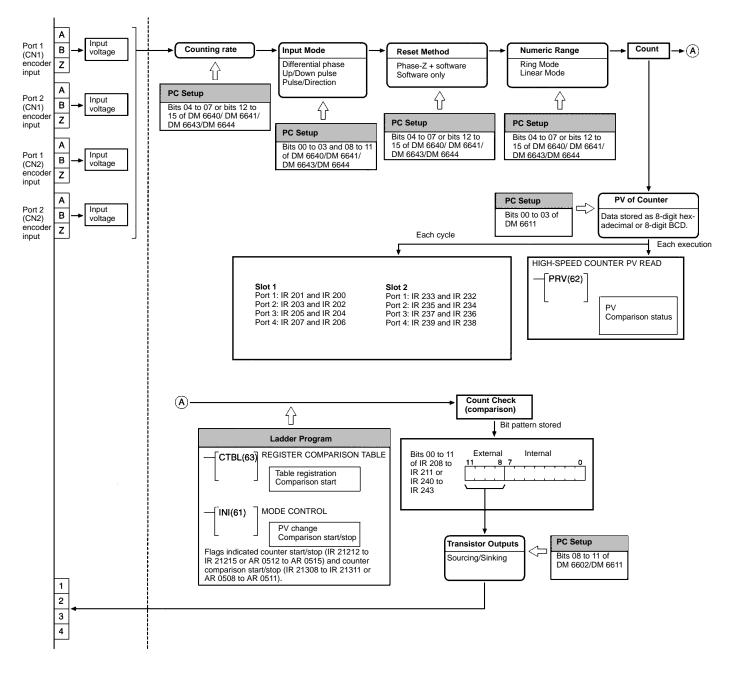

The High-speed Counter Board counts pulse signals entering through ports 1 to 4 from rotary encoders and outputs internal/external output bit patterns according to the number of pulses counted. The four ports can be used independently. An outline of the processing performed by high-speed counters 1 to 4 is provided below.

## **Overview of Process**

Input Signals and Input Modes

High-speed counters 1 to 4 can be set to different Input Modes in response to the type of signal input.

#### Differential Phase Mode (Counting Speed: 25 kHz or 250 kHz)

Two phase signals (phase A and phase B) with phase difference multiples of 1x, 2x, or 4x are used together with a phase-Z signal for inputs. The count is incremented or decremented according to differences in the two phase signals.

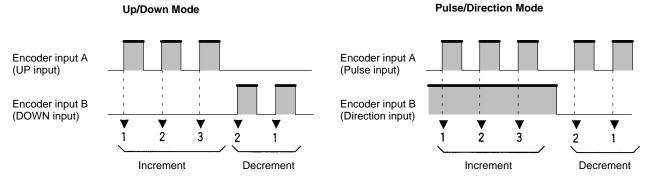

#### Up/Down Mode (Counting Speed: 50 kHz or 500 kHz)

Phase A is the incrementing pulse and phase B is the decrementing pulse. The counter increments or decrements according to the pulse that is detected.

#### Pulse/Direction Mode (Counting Speed: 50 kHz or 500 kHz)

Phase A is the pulse signal and phase B is the direction signal. The counter increments when the phase-B signal is ON and decrements when it is OFF.

| Phase A      | Phase B      | 1x        | 2x        | 4x        |

|--------------|--------------|-----------|-----------|-----------|

| $\uparrow$   | L            | Increment | Increment | Increment |

| Н            | $\uparrow$   |           |           | Increment |

| $\downarrow$ | Н            |           | Increment | Increment |

| L            | $\downarrow$ |           |           | Increment |

| L            | $\uparrow$   |           |           | Decrement |

| $\uparrow$   | Н            |           | Decrement | Decrement |

| Н            | $\downarrow$ |           |           | Decrement |

| $\downarrow$ | L            | Decrement | Decrement | Decrement |

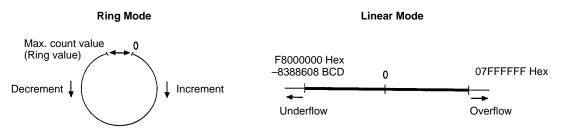

#### Numeric Ranges

The values counted by high-speed counters 1 to 4 can be counted using the following two range settings:

#### Ring Mode

In Ring Mode, the maximum value of a numerical range can be set using CTBL(63), and when the count is increment beyond this maximum value, it returns to zero. The count never becomes negative. Similarly, if the count is decremented from 0, it returns to the maximum value. The number of points on the ring is determined by setting the maximum value (i.e., the ring value) to a value between 1 and 8388607 BCD or between 1 and 7FFFFFF Hex. When the maximum value is set to 8388607, the range will be 0 to 8388607 BCD.

#### Linear Mode

In Linear Mode, the count range is always -8388608 to 8388607 BCD or F8000000 to 07FFFFF Hex. If the count decrements below -8388608 BCD or F8000000 Hex, an underflow is generated, and if it increments above 8388607 BCD or 07FFFFFF Hex, an overflow is generated.

If an overflow occurs, the PV of the count will remain at 08388607 BCD or 07FFFFF Hex, and if an underflow occurs, it will remain at F8388608 BCD or F8000000 Hex. In either case, counting and comparison will stop, but the comparison table will be retained in memory. The PV Overflow/Underflow Flag shown below will turn ON to indicate the underflow or overflow.

| Counter              | PV Overflow/Underflow Flag |          |  |

|----------------------|----------------------------|----------|--|

|                      | Slot 1                     | Slot 2   |  |

| High-speed counter 1 | IR 20814                   | IR 24014 |  |

| High-speed counter 2 | IR 20914                   | IR 24114 |  |

| High-speed counter 3 | IR 21014                   | IR 24214 |  |

| High-speed counter 4 | IR 21114                   | IR 24314 |  |

When restarting the counting operation, use the reset methods given below to reset high-speed counters 1 and 2. (Counters will be reset automatically when program execution starts and finishes.)

#### **Reset Methods**

The following two methods can be set to determine the timing at which the PV of the counter is reset (i.e., set to 0):

- Phase-Z signal + software reset

- Software reset

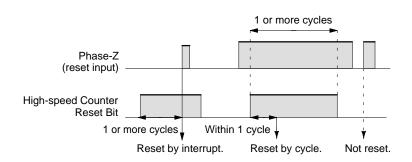

#### Phase-Z Signal (Reset Input) + Software Reset

The PV of the high-speed counter is reset in the first rising edge of the phase-Z signal after the corresponding High-speed Counter Reset Bit (see below) turns ON.

#### Software Reset

The PV is reset when the High-speed Counter Reset Bit turns ON. There are separate Reset Bits for each high-speed counter 1 to 4.

The Reset Bits of high-speed counters 1 to 4 are given in the following table.

| Counter              | Reset Bit |         |  |

|----------------------|-----------|---------|--|

|                      | Slot 1    | Slot 2  |  |

| High-speed counter 1 | IR 21200  | AR 0500 |  |

| High-speed counter 2 | IR 21201  | AR 0501 |  |

| High-speed counter 3 | IR 21202  | AR 0502 |  |

| High-speed counter 4 | IR 21203  | AR 0503 |  |

Reset Bits for high-speed counters 1 to 4 are refreshed only once each cycle. A Reset Bit must be ON for a minimum of 1 cycle to be read reliably.

**Note** The comparison table registration and comparison execution status will not be changed when the PV is reset. If a comparison was being executed before the reset, it will continue.

The following two methods are available to check the PV of high-speed counters 1 to 4. (These are the same methods as those used for built-in high-speed counter 0.)

- Target value method

- Range comparison method

Refer to page 31 for a description of each method.

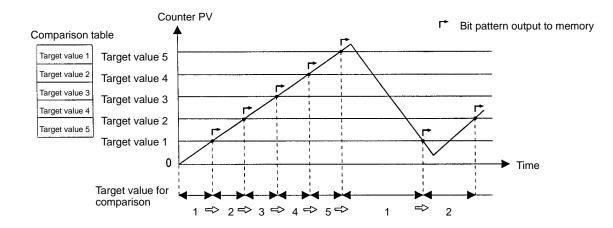

For the target value method, a maximum of 48 target values can be registered in the comparison table. When the PV of the counter matches one of the 48 regis-

Checking Methods for High-speed Counter Interrupts tered target values, the corresponding bit pattern (1 to 48) will be output to specific bits in memory.

When using target values, comparison is made to each target value in the order of the comparison table until all values have been met, and then comparison will return to the first value in the table. With the High-speed Counter Board, it does not make any difference if the target value is reached as a result of incrementing or decrementing the PV.

**Note** With high-speed counter 0 in the CPU Unit or high-speed counter 1 or 2 on the Pulse I/O Board or Absolute Encoder Interface Board, the leftmost bit of the word containing the subroutine number in the comparison table determines if target values are valid for incrementing or for decrementing the PV.

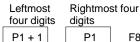

Examples of comparison table operation and bit pattern outputs are shown in the following diagrams.

## High-speed Counter Board

#### Section 2-1

Comparison values 1 through 48 and bit patterns 1 through 48 are registered in the target value table. Of bits 00 to 11 of each of these bit patterns, bits 0 to 7 are stored as internal output bits, and bits 08 to 11 are stored as external output bits. As shown in the diagram below, the bits in the external bit pattern are used in an OR operation on the corresponding bits of high-speed counters 1 to 4, the results of which are then output as external outputs 1 to 4.

Example:

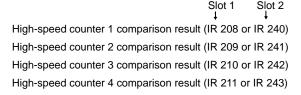

Slot 1 Slot 2 High-speed counter 1 comparison result (IR 208 or IR 240) High-speed counter 2 comparison result (IR 209 or IR 241) High-speed counter 3 comparison result (IR 210 or IR 242) High-speed counter 4 comparison result (IR 211 or IR 243)

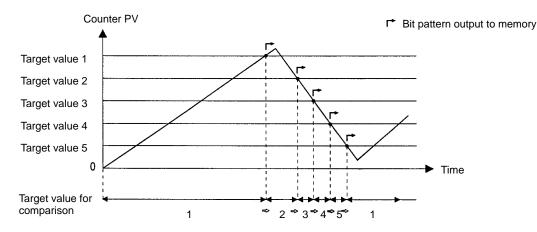

For the range comparison method, 16 comparison ranges are registered in the comparison table. When the PV of the counter first enters between the upper

68

Comparison range 4 Comparison range 3 Section

2-1

Bit pattern output when PV is inside a range. Comparison Lower limit 1 to upper limit 1 Bit pattern 1 Lower limit 2 to upper limit 2 PV of high-speed counter Bit pattern 2 Lower limit 16 to upper limit 16 Bit pattern 16 87 11 IR 208 to IR 211 or IR 240 to IR 243 External Internal output output bits bits (8 bits) An OR is taken of corresponding bits of IR 208 to IR 211, or IR 240 to IR 243. External outputs (four outputs) Bit pattern output to memory Counter PV Comparison table Comparison range 1 Comparison range 2 Comparison range 3 Comparison range 2 1 Comparison range 4 Comparison range 1 Time (s) The PV is continually compared to all comparison ranges.

and lower limits of one of the ranges 1 to 16, the corresponding bit pattern (1 to 16) will be output once to specific bits in memory.

Lower and upper limits for ranges 1 through 16 and bit patterns 1 through 16 are

registered in the range comparison table. Of bits 0 to 11 of each of these bit patterns, bits 0 to 7 are stored as internal output bits, and bits 8 to 11 are stored as external output bits. As shown in the diagram below, the bits in the external bit pattern are used in an OR operation on the corresponding bits of high-speed counters 1 to 4, the results of which are then output as external outputs 1 to 4.

Example:

External outputs 1 to 4 are controlled by ORs performed on corresponding bits (i.e., bits with the same bit number) in the comparison result bits 08 to 11 for high-speed counters 1 to 4. The user must determine which outputs should be turned ON for each possible comparison result and set the bit patterns so that the OR operations will produce the desired result.

**Note** Range Comparison Flags are supported by the built-in high-speed counter (high-speed counter 0) and the Pulse I/O Board for ranges1 to 8. These flags, however, are not supported by the High-speed Counter Board. The internal bit patterns must be used to produce the same type of output result.

# Reading High-speed<br/>Counter StatusThe following two methods can be used to read the status of high-speed count-<br/>ers 1 to 4:

- Using CPU Unit memory words

- Using PRV(62)

#### Using CPU Unit Memory Words

The memory area words and bits in the CPU Unit that indicate the status of highspeed counters 1 to 4 are given below.

#### **Inner Board Error Codes**

| Wo     | ord    | Bits     | Function                                                               |                                                        |

|--------|--------|----------|------------------------------------------------------------------------|--------------------------------------------------------|

| Slot 1 | Slot 2 |          |                                                                        |                                                        |

| AR 04  |        | 00 to 07 | Slot 1 The following 2-digit error codes are stored.<br>00 Hex: Normal |                                                        |

|        |        | 08 to 15 | Slot 2                                                                 | 01 or 02 Hex: Hardware error<br>03 Hex: PC Setup error |

#### **Operating Status Words**

| High-speed counter   | Word   |        |

|----------------------|--------|--------|

|                      | Slot 1 | Slot 2 |

| High-speed counter 1 | IR 208 | IR 240 |

| High-speed counter 2 | IR 209 | IR 241 |

| High-speed counter 3 | IR 210 | IR 242 |

| High-speed counter 4 | IR 211 | IR 243 |

The functions of the bits in each operating status word are as follows:

| Bits     | Function                                                                                                                       |

|----------|--------------------------------------------------------------------------------------------------------------------------------|

| 00 to 07 | Comparison Results: Internal Output Bits                                                                                       |

| 08 to 11 | Comparison Results: External Output Bits for Outputs 1 to 4                                                                    |

|          | The result of an OR operation on bits in same bit positions for all the high-speed counters 1 to 4 will be output. (See note.) |

| 12       | Counter Operating Flag (0: Stopped; 1: Running)                                                                                |

| 13       | Comparison Flag (0: Stopped; 1: Running)                                                                                       |

| 14       | PV Overflow/Underflow Flag (0: No; 1: Yes)                                                                                     |

| 15       | SV Error Flag (0: Normal; 1: Error)                                                                                            |

**Note** The following table shows the relationship between external outputs 1 to 4 and Comparison Results External Output Bits.

| High-speed<br>counter | External output   | Slot 1                               | Slot 2                               |

|-----------------------|-------------------|--------------------------------------|--------------------------------------|

| Counter 1             | External output 1 | OR of bits 08 of<br>IR 208 to IR 211 | OR of bits 08 of<br>IR 240 to IR 241 |

| Counter 2             | External output 2 | OR of bits 09 of<br>IR 208 to IR 211 | OR of bits 09 of<br>IR 240 to IR 241 |

| Counter 3             | External output 3 | OR of bits 10 of<br>IR 208 to IR 211 | OR of bits 10 of<br>IR 240 to IR 241 |

| Counter 4             | External output 4 | OR of bits 11 of<br>IR 208 to IR 211 | OR of bits 11 of<br>IR 240 to IR 241 |

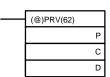

#### Using PRV(62)

The status of high-speed counters 1 to 4 can be read using PRV(62) in the manner shown below.

P: Port specifier C: 001 D: First destination word

| High-speed counter   | Value specified in P |        |

|----------------------|----------------------|--------|

|                      | Slot 1               | Slot 2 |

| High-speed counter 1 | 101                  | 001    |

| High-Speed counter 2 | 102                  | 002    |

| High-speed counter 3 | 103                  | 003    |

| High-speed counter 4 | 104                  | 004    |

The meaning of the individual bits of D, in which the status of high-speed counters 1 to 4 is stored, is given in the following table.

| Bits     | Function                                                                                                                       |

|----------|--------------------------------------------------------------------------------------------------------------------------------|

| 00 to 07 | Comparison Results: Internal Output Bits                                                                                       |

| 08 to 11 | Comparison Results: External Output Bits for Outputs 1 to 4                                                                    |

|          | The result of an OR operation on bits in same bit positions for all the high-speed counters 1 to 4 will be output. (See note.) |

| 12       | Counter Operating Flag (0: Stopped; 1: Running)                                                                                |

| 13       | Comparison Flag (0: Stopped; 1: Running)                                                                                       |

| 14       | PV Overflow/Underflow Flag (0: No; 1: Yes)                                                                                     |

| 15       | SV Error Flag (0: Normal; 1: Error)                                                                                            |

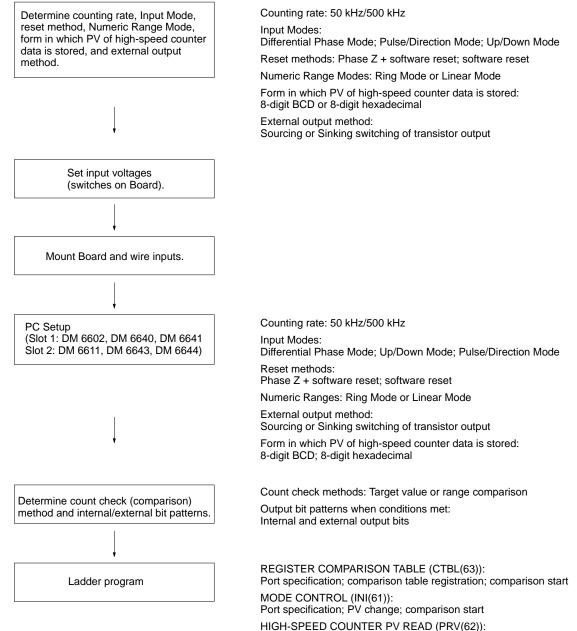

## Procedure for Using High-speed Counters

Reading PV of high-speed counter and status of comparison.

## High-speed Counter Board

**High-speed Counter Function**

## Preliminary PC Setup Settings

To use high-speed counters 1 to 4, make the following settings in PROGRAM mode.

#### Data Format and Sourcing/Sinking Setting for External Outputs

Slot 1: DM 6602 Slot 2: DM 6611 External Outputs 1 to 4 Transistor Selector 0 Hex: Sourcing (PNP) 1 Hex: Sinking (NPN) High-speed Counters 1 to 4 PV Data Format 0 Hex: 8-digit hexadecimal (BIN) 1 Hex: 8-digit BCD Default: 0000 (8-digit hexadecimal and sourcing (PNP))

#### Input Mode, Count Frequency, Numeric Range Mode, and Counter Reset Method

High-speed counter 1 Slot 1: Bits 00 to 07 of DM 6640 Slot 2: Bits 00 to 07 of DM 6643 High-speed counter 2 Slot 1: Bits 08 to 15 of DM 6640 Slot 2: Bits 08 to 15 of DM 6643 High-speed counter 3 Slot 1: Bits 00 to 07 of DM 6641 Slot 2: Bits 00 to 07 of DM 6644 High-speed counter 4 Slot 1: Bits 08 to 15 of DM 6641 Slot 2: Bits 08 to 15 of DM 6644

2 Hex: 4x Differential phase input

- 3 Hex: Up/Down pulse input

- 4 Hex: Pulse/Direction input

Default: 0000 (1x differential phase input, 50 kHz, Linear Mode, phase-Z + software reset)

| Count Frequency,<br>Numeric Range Mode,<br>and Reset Method | Value | Count<br>frequency | Numeric Range<br>Mode | Counter reset<br>method  |

|-------------------------------------------------------------|-------|--------------------|-----------------------|--------------------------|

|                                                             | 0 Hex | 50 KHz             | Linear Mode           | Phase Z + software reset |

|                                                             | 1 Hex |                    |                       | Software reset only      |

|                                                             | 2 Hex |                    | Ring Mode             | Phase Z + software reset |

|                                                             | 3 Hex |                    |                       | Software reset only      |

|                                                             | 4 Hex | 500 KHz            | Linear Mode           | Phase Z + software reset |

|                                                             | 5 Hex |                    |                       | Software reset only      |

|                                                             | 6 Hex |                    | Ring Mode             | Phase Z + software reset |

|                                                             | 7 Hex |                    |                       | Software reset only      |

#### <u>Usage</u>

High-speed counters are programmed as follows:

• The count operation is started as soon as valid settings are made.

- The PV is reset to 0 when power is turned ON and when program execution is started or stopped.

- The count operation alone does not start the comparison operation with the comparison table.

- The PV can be monitored using the words shown in the following table.

| High-speed counter   | Word           |                |  |

|----------------------|----------------|----------------|--|

|                      | Slot 1         | Slot 2         |  |

| High-speed counter 1 | IR 200, IR 201 | IR 232, IR 233 |  |

| High-speed counter 2 | IR 202, IR 203 | IR 234, IR 235 |  |

| High-speed counter 3 | IR 204, IR 205 | IR 236, IR 237 |  |

| High-speed counter 4 | IR 206, IR 207 | IR 238, IR 239 |  |

#### **Starting Comparison Operation**

The comparison table is registered in the CQM1H and the comparison started with CTBL(63). Comparison can also be started using the relevant control bits (IR 21208 to IR 21211 for slot 1 AR 0508 to AR 0511 for slot 2).

#### Starting Comparison with CTBL(63)

(@)CTBL(63) P: Port

| (@)CTBL(63) |    |  |

|-------------|----|--|

|             | Ρ  |  |

|             | С  |  |

|             | ΤB |  |

|             |    |  |

C: Mode

000: Target value table registration and comparison start 001: Range comparison table registration and comparison start 002: Target value table registration only 003: Range comparison table registration only

TB: First word of comparison table

| High-speed counter   | Value specified in P |        |

|----------------------|----------------------|--------|

|                      | Slot 1               | Slot 2 |

| High-speed counter 1 | 101                  | 001    |

| High-speed counter 2 | 102                  | 002    |

| High-speed counter 3 | 103                  | 003    |

| High-speed counter 4 | 104                  | 004    |

Setting 000 as the value of C registers a target value comparison table, and setting 001 registers a range comparison table. Comparison begins upon completion of this registration. While comparison is being executed, a bit pattern is stored as internal output bits and external output bits, as determined by the comparison table. Refer to the description of CTBL(63) for details on comparison table registration.

**Note** Although setting the value of C to 002 registers a target value comparison table, and setting C to 003 registers a range comparison table, comparison does not start automatically for these values. A control bit or INI(61) must be used to start the comparison operation.

#### **Starting Comparison with Control Bits**

The comparison operation will start when the bit corresponding to the highspeed counter in IR 21208 to IR 21211 for slot 1 or AR 0508 to AR 0511 for slot 2 is turned ON. It is necessary to have registered a comparison table beforehand. Comparisons cannot be performed in PROGRAM mode.

**Note** The High-speed Counter Board outputs the results of comparison as bit patterns to specific bits in memory, and does not execute interrupt subroutines. Bit patterns consist of internal bits and external bits, and the external bits are output on external output 1 to 4.

#### **Stopping Comparison Operation**

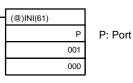

To halt a comparison operation, execute INI(61) as shown below. Halting a comparison can also be accomplished using a control bit.

#### Stopping Comparison with INI(61)

| High-speed counter   | Value set in P |        |  |

|----------------------|----------------|--------|--|

|                      | Slot 1         | Slot 2 |  |

| High-speed counter 1 | 101            | 001    |  |

| High-speed counter 2 | 102            | 002    |  |

| High-speed counter 3 | 103            | 003    |  |

| High-speed counter 4 | 104            | 004    |  |

#### **Stopping Comparison with Control Bits**

The comparison operation will stop when the bit corresponding to the highspeed counter in IR 21208 to IR 21211 for slot 1 or AR 0508 to AR 0511 for slot 2 is turned OFF.

- **Note** 1. To restart a comparison, either execute INI(61) with the port number as the first operand and 000 (execute comparison) as the second operand, or change the status of the control bit from 0 to 1.

- 2. Once a table has been registered, it is retained in the CQM1H throughout the operation (i.e., while a program is running) until a new table is registered.

The following two methods can be used to read the PVs of the high-speed counters 1 to 4:

- Reading the PV words in memory

- Using PRV(62)

#### Reading PV Words in Memory

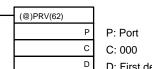

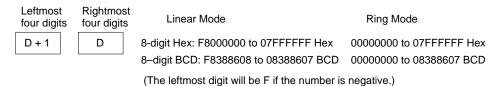

The PVs of high-speed counters 1 to 4 are stored in memory in the following way. The form in which the PV data is stored is determined by the setting of bits 00 to 03 of DM 6602 for slot 1, and DM 6611 for slot 2. The default setting is 8-digit hexadecimal.

| Slot 1: | Leftmost four di | gits Rightmost four di | igits                                                                                                                  |

|---------|------------------|------------------------|------------------------------------------------------------------------------------------------------------------------|

| Po      | ort 1 IR 201     | IR 200                 | Linear Mode Ring Mode                                                                                                  |

| Po      | ort 2 IR 203     | IR 202                 | 8-digit Hex: F8000000 to 07FFFFF Hex 00000000 to 07FFFFF Hex<br>8-digit BCD: F8388608 to 08388607 00000000 to 08388607 |

| Po      | ort 3 IR 205     | IR 204                 |                                                                                                                        |

| Po      | ort 4 IR 207     | IR 206                 | (The leftmost digit will be F if the number is negative.)                                                              |

Slot 2:

Reading the PVs

Leftmost four digits

Rightmost four digits

| -      | Linear Mode                                | Ring Mode                  |

|--------|--------------------------------------------|----------------------------|

| IR 232 | 8-digit Hex: F8000000 to 07FFFFFF He       | < 00000000 to 07FFFFFF Hex |

| IR 234 | 8-digit BCD: F8388608 to 08388607          | 00000000 to 08388607       |

| IR 236 | (The leftmost digit will be F if the numbe | r is negative.)            |

| IR 238 |                                            | <b>0</b> ,                 |

**Note** These words are refreshed only once every cycle, so the value read may differ slightly from the actual PV.

#### Using PRV(62)

PRV(62) can also be used to read the PVs of high-speed counters 1 to 4.

D: First destination word

| High-speed counter No. | Value specified in P |        |  |

|------------------------|----------------------|--------|--|

|                        | Slot 1               | Slot 2 |  |

| High-speed counter 1   | 101                  | 001    |  |

| High-speed counter 2   | 102                  | 002    |  |

| High-speed counter 3   | 103                  | 003    |  |

| High-speed counter 4   | 104                  | 004    |  |

The PVs of high-speed counters 1 to 4 are stored as shown in the following diagram.

Note PRV(62) reads the current PV when it is executed.

**Changing PVs**

The following 2 methods can be used to change the PVs of high-speed counters 1 to 4:

- Reset the counter (i.e., setting the counter to 0) using one of the reset methods

- Using INI(61)

The following is an explanation of the use of INI(61). Refer to Reset Methods on page 65 for an explanation of the use of the reset methods.

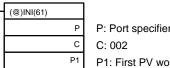

#### Changing PV with INI(61)

INI(61) is used to change the PV of high-speed counters 1 to 4.

| - | P: Port specifier |

|---|-------------------|

| 2 | C: 002            |

| 1 | P1: First PV word |

| High-speed counter No. | Value specified in P |        |

|------------------------|----------------------|--------|

|                        | Slot 1               | Slot 2 |

| High-speed counter 1   | 101                  | 001    |

| High-speed counter 2   | 102                  | 002    |

| High-speed counter 3   | 103                  | 003    |

| High-speed counter 4   | 104                  | 004    |

**Ring Mode**

**Ring Mode**

F8000000 to 07FFFFFF Hex

00000000 to 07FFFFF Hex 00000000 to 08388607 BCD

(The leftmost digit will be F Hex if the number is negative.)

F8388608 to 08388607 BCD

**Note** After matching the final target value in a target value comparison table, the comparison process returns automatically to the first target value in the table. Therefore, following completion of a sequence of comparisons, the process can be repeated by initializing the PV.

**Stopping and Restarting the Counting Operation** It is possible to stop the counting operation of one of the high-speed counters 1 to 4 by turning ON a control bit. The PV of the counter will be retained.

The counting operation can be stopped by turning ON bits 12 to 15 of IR 212 for slot 1 or AR 05 for slot 2. These bits correspond to high-speed counters 1 to 4. Turn OFF these bits to restart the counting operation. The high-speed counter will restart from the value at which it was stopped.

**Note** The Counter Operating Flag can be used to determine whether the count operation is running or stopped (0: Stopped; 1: Operating).

| High-speed counter   | Counter Operating Flag |          |

|----------------------|------------------------|----------|

|                      | Slot 1                 | Slot 2   |

| High-speed counter 1 | IR 20812               | IR 24012 |

| High-speed counter 2 | IR 20912               | IR 24112 |

| High-speed counter 3 | IR 21012               | IR 24212 |

| High-speed counter 4 | IR 21112               | IR 24312 |

## Examples

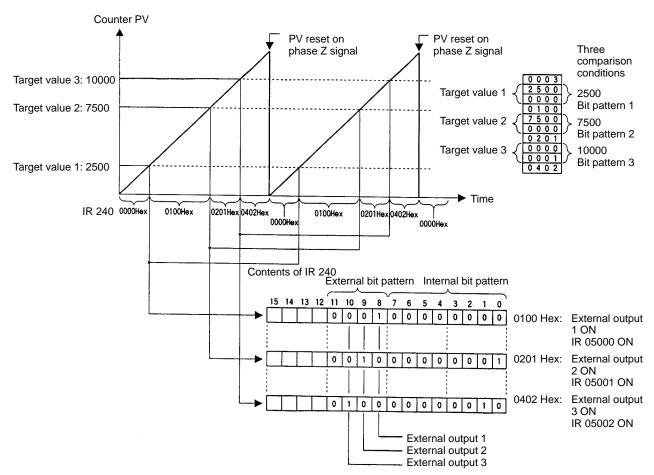

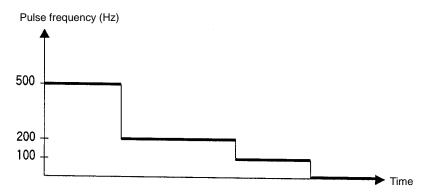

The following example illustrates the use of high-speed counter 1 on a Highspeed Counter Board mounted in slot 2. Target value comparison is performed to turn ON bits in the internal/external bit patterns stored in memory according to the PV of the counter. The status of the internal output bits is used to control the frequency of a contact pulse output.

The Reset Bit is kept ON in the program so that the PV of the counter is reset on the phase Z signal after the last target value has been reached.

Before running the program, the PC Setup should be set as shown below, and the CQM1H restarted to enable the new setting in DM 6611.

DM 6611: 0001 (Sourcing outputs for external outputs 1 to 4, 8-digit BCD for PV storage of high-speed counters 1 to 4)